Η Đài Loan kinh tế hàng ngày Ông tuyên bố rằng TSMC đạt được một khám phá nội bộ quan trọng để xử lý cuối cùng công nghệ in thạch bản 2 nm.

ΣTheo công bố, cột mốc quan trọng này cho phép TSMC lạc quan về việc triển khai sản xuất sớm "Sản xuất rủi ro" 2 nm vào năm 2023.

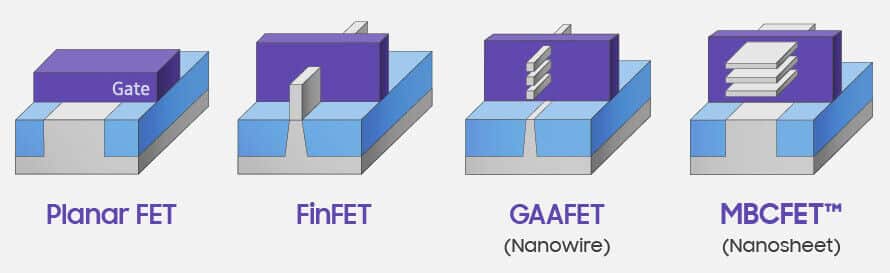

Vẫn còn ấn tượng là các báo cáo rằng TSMC từ bỏ công nghệ FinFet cho bóng bán dẫn hiệu ứng trường kênh đa cầu (MBCFET) mới dựa trên công nghệ Gate-All-Around (GAA). Khám phá quan trọng này sắp đến một năm sau khi TSMC thành lập một nhóm trong nhà, với mục tiêu là mở đường cho sự phát triển của kỹ thuật in thạch bản 2 nm.

Công nghệ MBCFET mở rộng kiến trúc GAAFET bằng cách lấy bóng bán dẫn hiệu ứng trường Nanowire và "trải rộng" nó để trở thành một Nanosheet. Ý tưởng chính là tạo ra bóng bán dẫn hiệu ứng trường XNUMXD.

Bóng bán dẫn bán dẫn oxit kim loại bổ sung mới này có thể cải thiện khả năng kiểm soát mạch và giảm rò rỉ dòng điện. Triết lý thiết kế này không dành riêng cho TSMC - Samsung có kế hoạch phát triển một biến thể của thiết kế này trong công nghệ in thạch bản của họ 3 nm.

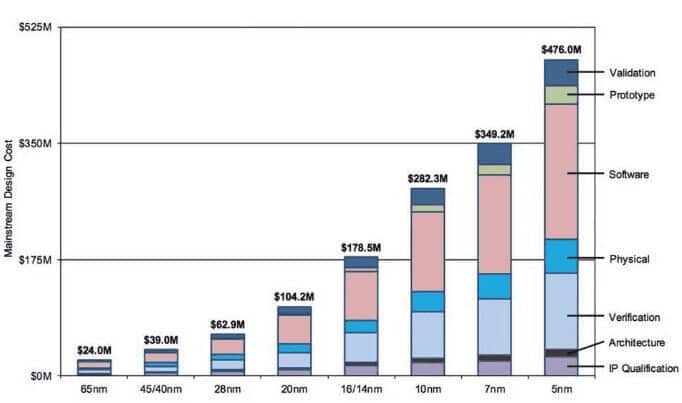

Như thường lệ, giảm hơn nữa quy mô sản xuất chip đi kèm với một chi phí rất lớn. Cụ thể, chi phí phát triển cho máy in thạch bản 5 nm đã lên tới 476 triệu USD, trong khi Samsung tuyên bố rằng công nghệ GAA 3 nm sẽ có giá hơn 500 triệu đô la. Tất nhiên, sự phát triển của kỹ thuật in thạch bản 2 nm, sẽ vượt quá những số tiền này…

Các bạn đừng quên theo dõi nhé Xiaomi-miui.gr tại Google Tin tức để được thông báo ngay lập tức về tất cả các bài viết mới của chúng tôi!

Các bạn đừng quên theo dõi nhé Xiaomi-miui.gr tại Google Tin tức để được thông báo ngay lập tức về tất cả các bài viết mới của chúng tôi!